# Foundry WLSI Technology for Power Management System Integration

Chuei-Tang Wang, Chih-Lin Chen, Jeng-Shien Hsieh, Victor C.Y. Chang, Douglas Yu

R&D,TSMC

Oct. 2016

2016 PwrSoC

© 2016 TSMC, Ltd

**Open Innovation Platform®**

### Outline

### Motivation

- PMIC system integration trends

- Foundry WLSI technology Portfolio

### High Performance Computing System (HPC) on CoWoS

- VR on CoWoS

- Impact of Si interposer

- Mobile AP and PMIC System (MAPS) on InFO

- Power Delivery Network

- PVR on InFO

### Summary & Outlook

2016 PwrSoC

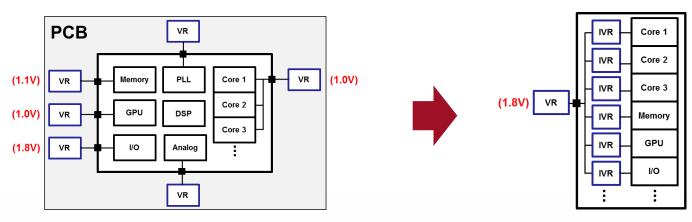

## Motivation: High Efficiency Power Management System

### • PMIC System Trend:

- System on PCB → System on SoC/Package

- Shared Voltage → Per-core Voltage Control

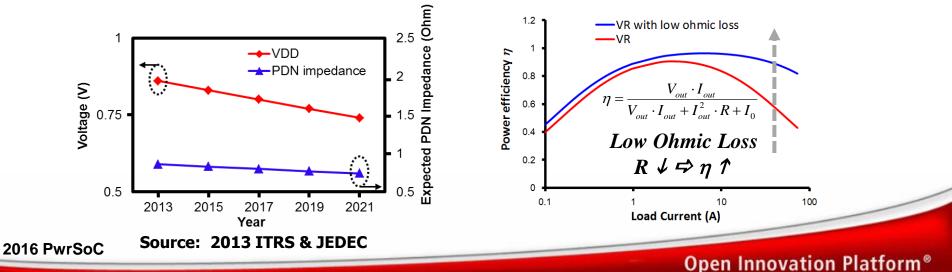

- $V_{dd}$  Scaling  $\rightarrow$  Low PDN Impedance Needed

- Long Battery Life → High Efficiency Voltage Regulator

- **System on PCB**  $\rightarrow$  System on SoC/Package

### Motivation: High Efficiency Power Management System

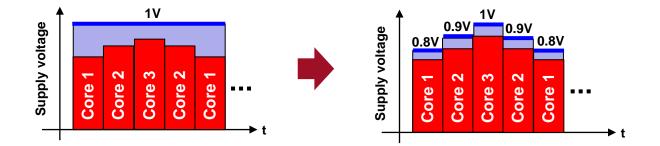

### Shared voltage → Per-core voltage control

- **V**<sub>dd</sub> Scaling  $\rightarrow$  0.74V  $\rightarrow$  Low PDN Impedance

- Long Battery Life  $\rightarrow$  High Efficiency VR  $\rightarrow$  Low Ohmic Loss

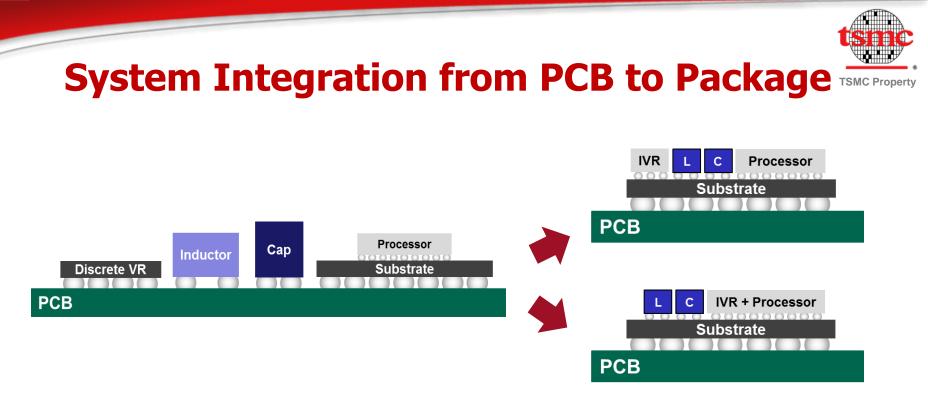

### Benefits from System on Package

- PDN path: Long  $\rightarrow$  Short

- Discrete component number: Dozen  $\rightarrow$  Several

- Switching frequency: 10 MHz  $\rightarrow$  100 MHz

- L: µH → nH

- > C:  $\mu$ F → nF

- Form factor: Large  $\rightarrow$  Small

2016 PwrSoC

5

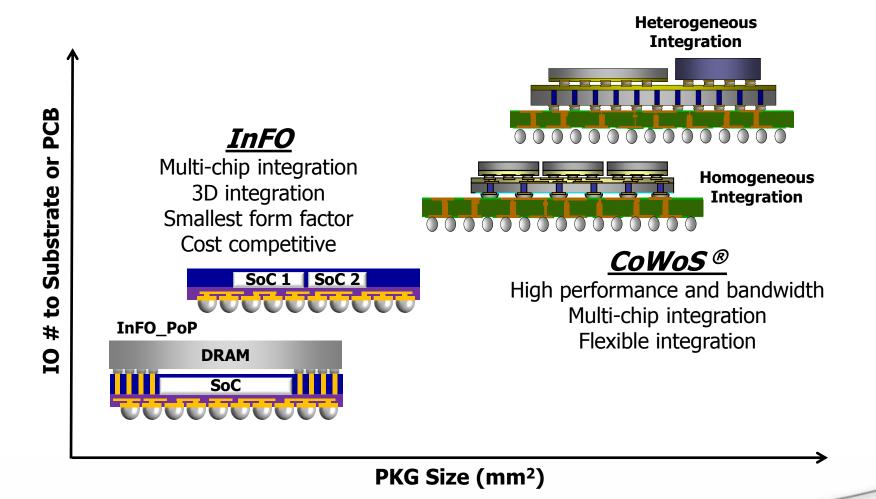

### TSMC WLSI Technology Platforms from low cost to high performance

2016 PwrSoC \* WLSI: Wafer Level System Integration

© 2016 TSMC, Ltd

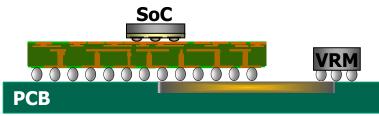

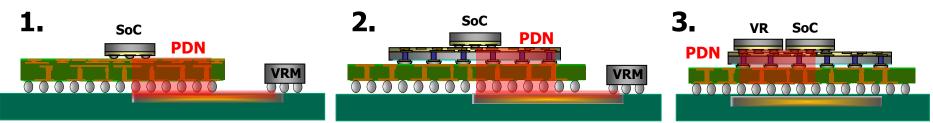

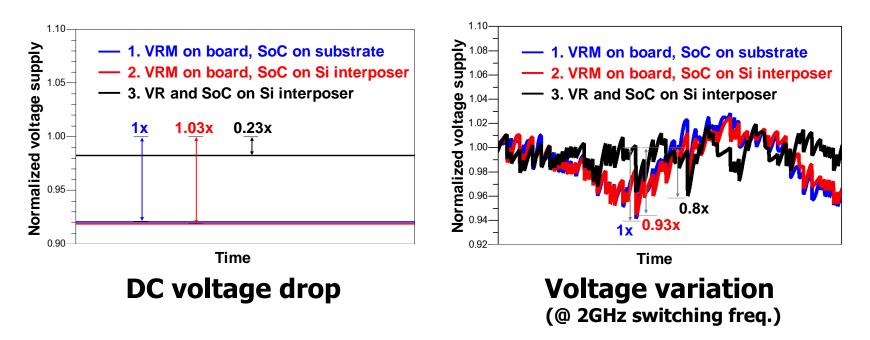

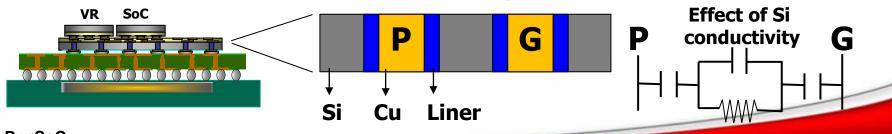

• System 1: VRM on board, SoC on substrate (FCBGA)

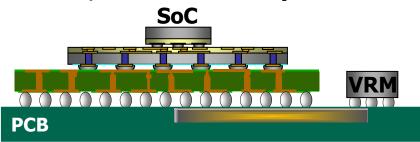

• System 2: VRM on board, SoC on Si interposer

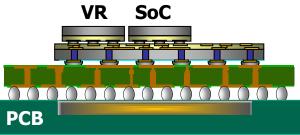

• System 3: VR and SoC on Si interposer

#### **Open Innovation Platform®**

© 2016 TSMC, Ltd

# SoC and VR(M) System Design on CoWoS

#### System 1: VRM on board, SoC on substrate

- PDN path: VRM  $\rightarrow$  PCB  $\rightarrow$  Substrate  $\rightarrow$  SoC

- PDN L/W: PCB/50/5 mm, Substrate/12/4 mm

- PDN metal layer: PCB/2, Substrate/10

#### • System 2: VRM on board, SoC on Si interposer

- PDN path: VRM  $\rightarrow$  PCB  $\rightarrow$  Substrate  $\rightarrow$  Si Interposer  $\rightarrow$  SoC

- PDN L/W: PCB/50/5 mm, Substrate/12/4 mm, Si interposer/12/4 mm

- PDN metal layer: PCB/2, Substrate/8, Si Interposer /2

#### System 3: VR and SoC on Si interposer

- PDN path: VR  $\rightarrow$  Si Interposer and Substrate  $\rightarrow$  SoC

- PDN L/W: Substrate/12/4 mm, Si interposer/12/4 mm

- PDN metal layer: Substrate/8, Si Interposer /2

#### FOM: PDN impedance, voltage drop and voltage variation

#### 2016 PwrSoC

© 2016 TSMC, Ltd

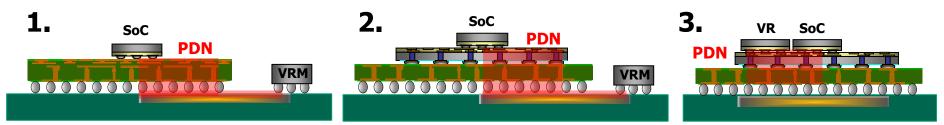

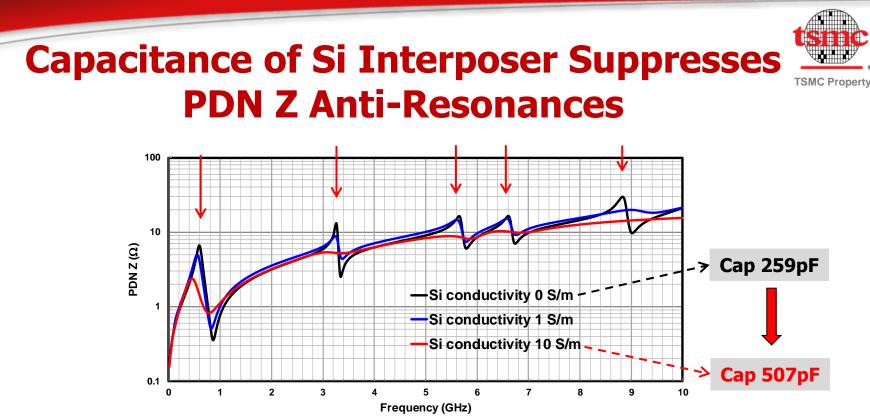

## PDN Impedance Reduction from Si Interposer

Interposer mitigates anti-resonance at high frequencies

Short interconnect reduces PDN impedance: DC and AC

Numbers of De-cap to be decreased

2016 PwrSoC

© 2016 TSMC, Ltd

**Open Innovation Platform®**

**TSMC** Property

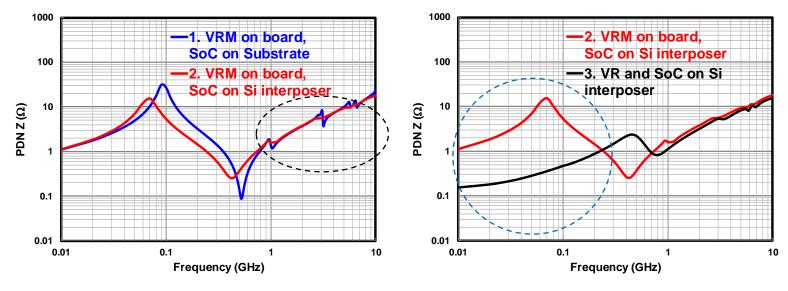

## Si Interposer Reduces Voltage Drop and Voltage Variation

- The voltage drop and voltage variation from VR to SoC  $\infty$  PDN Impedance

- The VR and SoC on Si interposer system

- DC voltage drop: 23% of VRM on board, SoC on substrate system

- Voltage variation: 80% of VRM on board, SoC on substrate system.

2016 PwrSoC

- High conductivity Si interposer suppresses the anti-resonances

- High Si conductivity → High TSV Liner capacitance → More suppression of PDN Z anti-resonance

#### **Cross section of TSV and equivalent circuits**

2016 PwrSoC

© 2016 TSMC. Ltd

**Open Innovation Platform®**

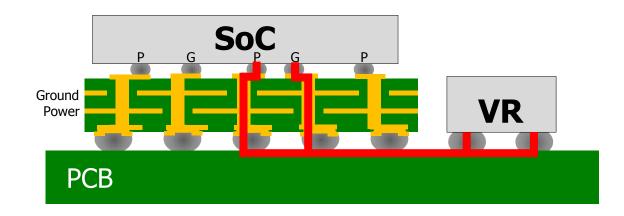

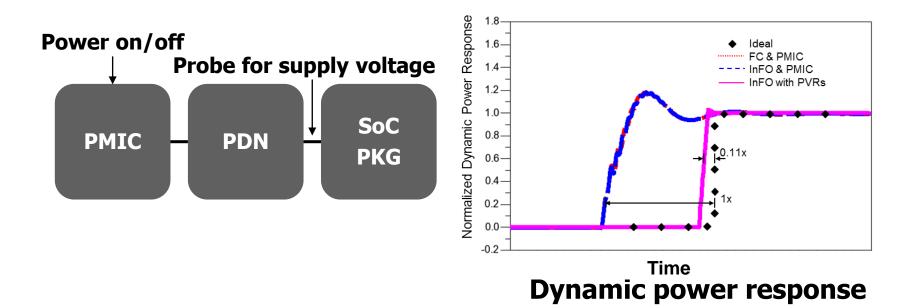

### SoC and VR(M) System Design on InFO for Mobile Products

System 1: FC and PMIC

System 2: InFO and PMIC

InFO and FC PKG

#### System 3: InFO with PVR

**Open Innovation Platform®**

#### • System 1: FC and PMIC

- PDN path: VRM  $\rightarrow$  PCB  $\rightarrow$  Substrate  $\rightarrow$  SoC

- PDN routing: in millimeter scale

#### • System 2: InFO and PMIC

- PDN path: VRM  $\rightarrow$  PCB  $\rightarrow$  InFO $\rightarrow$  SoC

- PDN routing: in millimeter scale

#### • System 3: InFO with partitioned VR (PVR)

- PDN path: VR  $\rightarrow$  InFO $\rightarrow$  SoC

- PDN routing: in micrometer scale

- FOM: PDN impedance, voltage drop, voltage variation, power response

2016 PwrSoC

**Open Innovation Platform®**

### **Power Integrity – PDN Impedance Calculation**

- PI: A measure for power supply stability; related to impedance of power distribution network (PDN)

- PDN impedance is  $Z_{PDN} = R + j\omega L + (\frac{1}{j\omega C} // Z_{VR})$ where  $Z_{VR}$  is the impedance of voltage regulator.

- Low R & L in PDN → Low  $Z_{PDN}$  → Better PI performance

2016 PwrSoC

13

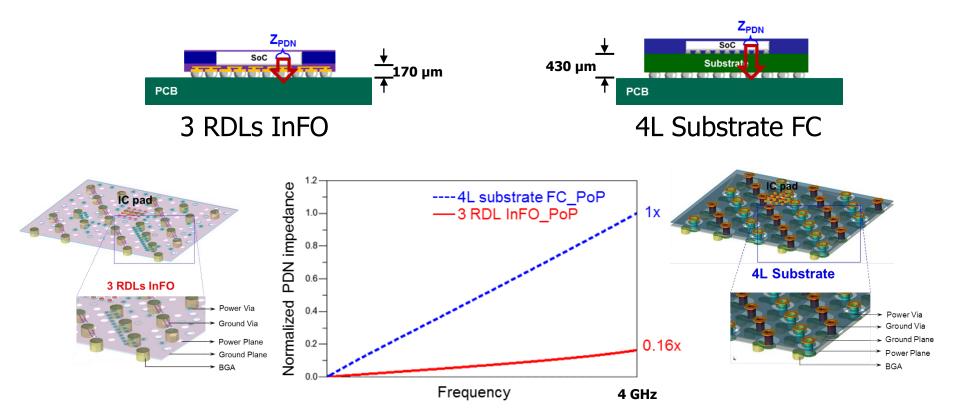

# Low PDN Impedance in InFO Package

- PDN impedance: InFO\_PoP is 16% of the FC\_PoP.

- InFO\_PoP: Substrate & C4 Bump eliminated and thin RDL

- Low PDN impedance → High power stability

2016 PwrSoC

14

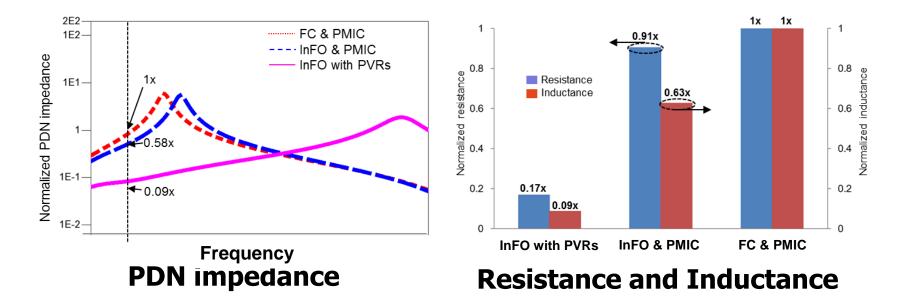

### **InFO with PVRs system**

- PDN impedance: 9% of FC & PMIC system

- Resistance: 17% of FC & PMIC system

- Inductance: 9% of FC & PMIC system

2016 PwrSoC

DC voltage drop

Voltage variation (ΔV)

- The voltage drop and voltage variation from VR to AP  $\propto$  PDN Impedance

- The InFO with PVRs system

- DC voltage drop: 17% of FC & PMIC system

- Voltage variation: 25% of FC & PMIC system

2016 PwrSoC

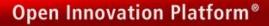

## Power Response for InFO + PVRs System

- Transient time: Time period for power on from 0 to 1 stable state

- The InFO with PVRs system

- Transient time: 11% of FC & PMIC system

2016 PwrSoC

© 2016 TSMC, Ltd

# **Summary of the PI Results**

| System specifications                               | PDN Z<br>@10MHz | PDN Z<br>@200MHz | Voltage<br>drop | Voltage variation |

|-----------------------------------------------------|-----------------|------------------|-----------------|-------------------|

| System 1: VRM on board,<br>SoC on substrate (FCBGA) | 1x              | 1x               | 1x              | 1x                |

| System 2: VRM on board,<br>SoC on Si interposer     | 1.01x           | 0.45x            | 1.03x           | 0.93x             |

| System 3: VR and SoC on<br>Si interposer            | 0.14x           | 0.27x            | 0.23x           | 0.8x              |

| System specifications | Resistance | Inductance | Voltage variation | Transient<br>time |

|-----------------------|------------|------------|-------------------|-------------------|

| InFO with PVRs        | 0.17x      | 0.09x      | 0.25x             | 0.11x             |

| InFO & PMIC           | 0.91x      | 0.63x      | 0.67x             | 1x                |

| FC & PMIC             | 1x         | 1x         | 1x                | 1x                |

#### 2016 PwrSoC

18

**Open Innovation Platform®**

## **Summary and Outlooks**

- Foundry WLSI technology, CoWoS and InFO, provides leading edge solutions for power management system integration.

- The technologies provide excellent PDN performance for low power consumption, low voltage drop and low voltage variation for system design.

- V<sub>dd</sub> scaling of SoC leads to power system design challenges

→ TSMC WLSI technology provides the design solution.

© 2016 TSMC, Ltd

# **Thanks for your attention!**

2016 PwrSoC

© 2016 TSMC, Ltd